## Discrete Boost

## © 2001 Jay Doyl e

## A DISCRETE OP AMP GAIN MACHINE

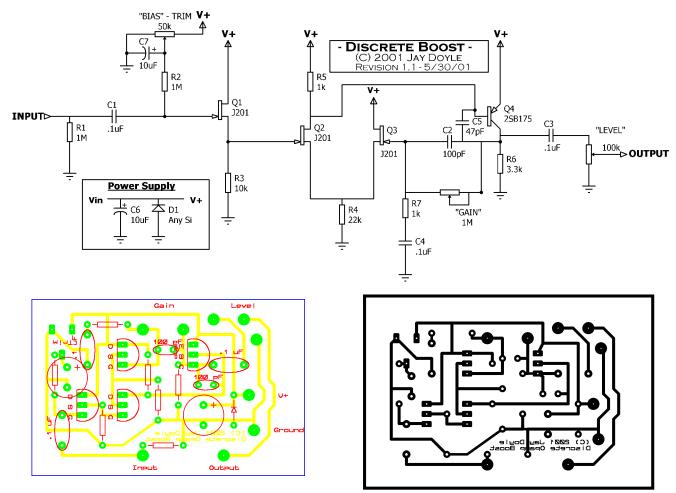

CIRCUIT DESCRIPTION: Input couples to Q1, configured as a source follower, through input coupling cap C1. R1 prevents clicks when using true bypass. R2 provides voltage bias to Q1, as well as the rest of the circuit, from the BIAS trim-pot, set up as a voltage divider between the positive supply and ground. Q1 is directly coupled to the gate of Q2. Q2, Q3 and Q4 comprise a minimal operational amplifier set up in a non-inverting amplifier configuration. Q2 and Q3 form a differential amplifier, the output of which is coupled from the drain of Q2 to the base of Q4, set up as a high gain, voltage amplifier. The gate of Q2 is the positive input and Q3's gate is the negative input for the op amp. The output of the operational amplifier is taken from the collector of Q4. C2 and C5 both serve to compensate the op amp to reduce oscillations in the upper frequencies. C2, C4, R7 and the "GAIN" pot make up the components in the feedback path and function the same as in an IC op amp configuration. The output of the operational amplifier is taken from Q4's collector and is coupled to the "LEVEL" pot through C3.

**DESIGN NOTES:** This design uses discrete components, instead of the conventional IC op amp, to achieve a clean to lightly overdriven boost. The characteristics of the overdriven sound will depend greatly upon the output transistor, Q4; if available, try a high hFE germanium transistor as Q4. Trim the "Bias" pot until the collector of Q4 is at  $\frac{1}{2}$  V+, for greatest headroom, or away from  $\frac{1}{2}$  V+ for asymmetrical clipping when overdriven. With JFETs comprising the differential amplifier, and using a Ge transistor with a gain of 200 as Q4, there was very light distortion, even at full gain. R6 and R4 may need to be adjusted to suit different transistors. C5 while serving to compensate the op amp, also sets the slew rate; raising it's value will cut highs, raising it's value significantly will induce slew rate limiting, drastically cutting highs and inducing a unique distortion.

**ETC.**: While having lower gain, higher CMRR and input offset voltage than conventional IC op amps, this circuits offers lower noise and ease of modification as well as the ability to use different types of transistors for different sound qualities. Use this as a clean boost to cut through the mix, to overdrive your amp, or push the gain up and utilize this circuit's smooth distortion. More importantly, try implementing this design in place of IC op amps and see if you can achieve some new and unique sounds!

| Part Number    | Value        | Notes                                     |

|----------------|--------------|-------------------------------------------|

| Resistors      |              |                                           |

| R1             | 1 Meg        | Pull down resistor                        |

| R2             | 1 Meg        | Bias resistor                             |

| R3             | 10k          | Source follower bias resistor             |

| R4             | 22k          | Sets current through differential pair    |

| R5             | 1k           | Gain/bias resistor for + input (optional) |

| R6             | 3k3          | Bias resistor for output gain stage       |

| R7             | 1k           | With C4, sets lo-freq roll off            |

| Capacitors     |              |                                           |

| C1             | .1 uF        | Input coupling cap                        |

| C2             | 100 pF       | Compensation cap                          |

| C3             | .1 uF        | Output coupling cap                       |

| C4             | .1 uF        | With R7, sets low-freq roll off           |

| C5             | 47 pF        | Compensation cap                          |

| C6             | 10 uF        | Power supply bypass cap                   |

| C7             | 10 uF        | Bias supply bypass cap                    |

| Pots           |              |                                           |

| Bias           | 50k (trim)   | Sets voltage bias for circuit through R2  |

| Gain           | 1 Meg        | Sets gain of discrete op amp              |

| Level          | 100k (log)   | Sets output level of circuit              |

| Semiconductors |              |                                           |

| Q1             | J201         | Input buffer, source follower             |

| Q2             | J201         | Gate is positive input of op amp          |

| Q3             | J201         | Gate is negative input of op amp          |

| Q4             | Any PNP      | Collector is output of op amp             |

| D1             | Any Si diode | Reverse polarity protection               |

Layout Shown Inside 2" x 3" Reference Box